|

|

|

|

論理回路(デジタル回路)記号

論理(デジタル)回路と

論理演算(ビット演算)の特別な関係

ながめていると楽しくなる記号(図=アイコン)です。

AND回路

OR回路

XOR回路

NOT回路

NAND回路

NOR回路

左方が入力側で、右方に出力します。つまり、左方に1つのビット値の0か1を入力し、論理ビット演算をした結果を右方に出力します。 「0か1」を「OFFかONや電圧Lowか電圧High」などの電気信号に読みかえてもかまいません。 デジタル回路記号ともいいます。実際には幾つかの回路をつなげて使います。

OR回路

XOR回路

NOT回路

NAND回路

NOR回路

左方が入力側で、右方に出力します。つまり、左方に1つのビット値の0か1を入力し、論理ビット演算をした結果を右方に出力します。 「0か1」を「OFFかONや電圧Lowか電圧High」などの電気信号に読みかえてもかまいません。 デジタル回路記号ともいいます。実際には幾つかの回路をつなげて使います。

例として AND回路をとりあげて調べましょう

AND回路で、入力 A , B 出力

C を示しています。 実際にはAND論理演算の規則(きそく)により、次のように4通りの場合があります。

AND回路で、入力 A , B 出力

C を示しています。 実際にはAND論理演算の規則(きそく)により、次のように4通りの場合があります。

|

A |

B |

A and B |

|

0 |

0 |

0 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

1 |

上の表(規則)に従い、このようになりますよ。他の論理回路 についてもそれぞれ同じですから確かめておいてください。

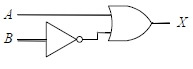

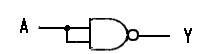

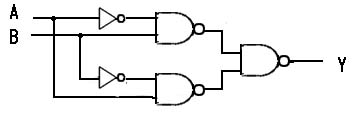

簡単な論理回路の例を2題考えてみます。

入力A,Bに対して、出力Xがどうなるかを表(真理値表)にしてみるとよいと思います。

回路は NOT、ORの2個をつなげています。順に真理値表を作ってみよう。

|

A |

B |

|

X=

A or |

|

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

1 |

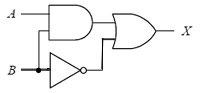

AND,NOT,ORの3回路をつないでいます。上の図のようにA' ,B'をけいさんするといいですよ。 出力Xは、上の問題とおなじになります。

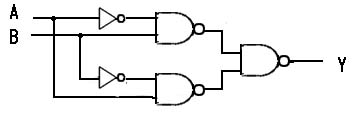

次の2つの論理回路は等価(出力Xが同じ)です。比べてみよう。

上図は、OR,NAND,AND回路をつなげています。

上次図は、NOT、AND,OR回路をつなげています。

|

A |

B |

A+B |

|

X |

|

0 |

0 |

0 |

1 |

0 |

|

0 |

1 |

1 |

1 |

1 |

|

1 |

0 |

1 |

1 |

1 |

|

1 |

1 |

1 |

0 |

0 |

|

A |

B |

|

|

A・ |

X | |

|

0 |

0 |

1 |

1 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

なお黒点のところでは接続しています。さて上の2つは出力Xが全く同じです。

これは XOR(排他的論理和) A

と同じです。 このように等価であるとき、次のように等式で表します。このような式を論理式といいます。 (A+B)・(

と同じです。 このように等価であるとき、次のように等式で表します。このような式を論理式といいます。 (A+B)・(ホントきれいな論理式です。

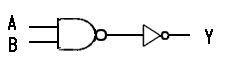

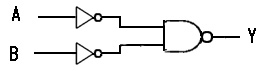

NAND回路とNOT回路のみ使い、

AND、OR、XOR回路を作る

論理回路では NAND がヒーロー &ヒロインです.

(1)

(1)は、出力YがAND回路と同じです。 つまり、NANDとNOTを使いANDを作っているのです。何面倒なことするなだって?

(2)

(2)は OR回路と同じです。実際に真理値表を書いて確かめて下さい。

(3)

(3)は、NAND回路からNOT回路が出来ました 。ということは、(1)(2)はNAND回路だけで書き直せるということにもなります。

(4)

(4)は、XOR回路と同じです。そして(3)により、NANDのみでXORを作ることが出来るわけです。

NANDは超すごい。未だ触れていない残ったNORもNANDのみで作ってみよう。

(4)は、XOR回路と同じです。そして(3)により、NANDのみでXORを作ることが出来るわけです。

NANDは超すごい。未だ触れていない残ったNORもNANDのみで作ってみよう。

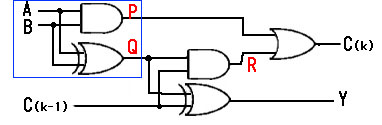

加算回路(全加算器)について

A, B 2入力の全加算回路です。A+B の結果をY に出力しますが、繰り上がり はC(k)にセットします。入力 C(k-1) は、下位の繰り上がりです。Cをキャリフラグといいます。

次表に真理値を出してあります。入力がA, Bに加えてC(k-1) の3個ですから、全部で8通りの場合があります。出力 Y

及び C(k)がたし算のルールに一致していることを確かめて下さい。

回路図の青枠部分は、半加算回路です。この場合は出力Pがキャリフラグに相当します。 半加算回路が2つ使われていることがわかります。さて上記のA, Bは1ビットの0 か1 ですから、上は1ビット限りの加算です。数ケタの数の加算は上の全加算器を数個つなげます。 例えば8ビット(1バイト)で表す数どうしを加算するには、8個つなげていることになります。その接続の様子は後日図示する予定です(^_^)。

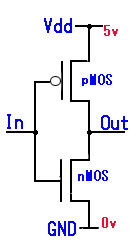

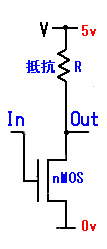

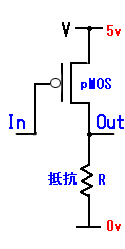

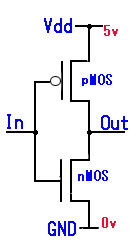

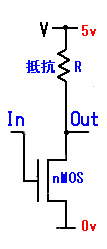

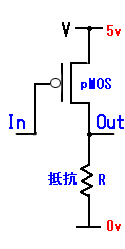

例として一番分かりやすいMOSトランジスタで作るNOTゲートを取り上げましょう。 集積回路(IC)ではスイッチ要素として、トランジスタを利用し電圧をHigh、Low (あるいは On、Off) と変化させることにより、入出力を制御(せいぎょ)するのが殆どです。 ここでは代表的なMOS型トランジスタを使います。 MOSトランジスタはとても小さく1つのICチップに数万個も埋め込まれることもある程です。

(1) In = 0ではpMOSが導電しOut = 1(Vdd接続)。

In = 1ではnMOSが導電しOut = 0 (GND接続)。

(2) In = 0ではnMOSがOFFで、Out = 1(V接続)。

In = 1ではONに変わりOut = 0(0v接続)。

(3)In = 0ではpMOSがONでOut = 1。

In = 1ではOFFに変わりOut = 0。

(1)(2)(3)いずれもNOTゲート回路であることが分かります。つまり入出力を反転させています。

Vddは電源(習慣的に+5v)、GNDはグランド (アースです = 0v )、Rは適当な抵抗、In=入力、Out=出力。

In に電圧が加えられていない状態では、pMOS トランジスタはON(=導電)、nMOSトランジスタはOFF です。逆に電圧が加えられると、pMOSはOFF、nMOSはON(=導電)になります。 トランジスタはスイッチと同じ働きをします。NOTゲートをインバータとも言います。<注> MOSトランジスタのゲート端子(左側)へは電流は発生しません。

電源Vdd に近い2個の pMOSは並列になっており、GNDに近い nMOS2個は直列になっていることに注意し 、起こりうるすべての場合を表にしました。

これは、論理回路NANDに他なりません。 このように実際にトランジスタを使って基本回路をつくり、さらには集積回路ICに取り入れ、幾つも組み合わせて複雑な電子回路ができあがります。

同様にしてMOSトランジスタを使い、その他の基本ゲートAND、OR、XORを作ってみよう。多入力(3入力以上)の場合も考えてみよう。

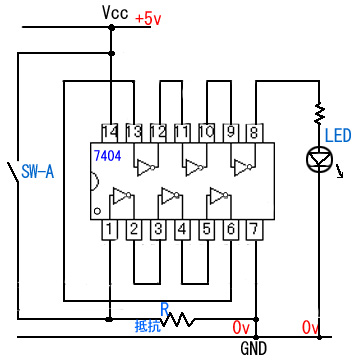

NOT IC

6個のNOT回路を入れた14PINのIC

(1→2)

NAND IC

2入力のNAND 回路4個を入れた14PINのIC

(1,2→3)

その形からムカデ、ゲジゲジ虫とも呼びます。そのICの代表例を上に示しました。 コンピュータや携帯、電化製品の中にある半導体基板(はんどうたいきばん)に多数のIC(集積回路しゅうせきかいろ)が埋め込まれています。 殆どブラックボックス化しています。どのように利用するのでしょう。

ブレッドボード(一種の半導体基板)上に各種パーツ、IC、コンデンサー、ダイオード、トランジスタ、コイル、抵抗などを並べて、さまざまな電子回路を実現するわけです。ここでは7404型という6個のNOT回路をもつ14PIN ICを図のように配線して実験を試みます。

ICを動作させるため電源を入れなければなりませんが、14番PIN=Vcc、7番PIN=GND と決められています。SW-A(スイッチA) をON (入力= 1) 、OFF (入力=0)と交互に切り替えると、LED(電球)が点灯(=1)、消灯(=0)を交互に繰り返す。ただそれだけです。これはICが良品か否かを検査するのに役立つというわけです。

ただ実験回路は上手く動作しなかった代物ですから信用無用で試さないでください(笑)。

答えは次のページへ。

この負数の絶対値(=正の数)を求めるため、

ビット列を反転して、1を加える操作をすると

11110100→00001011→00001100 となります。

問題の減算は、これを加算するということです。

コンピューターは減算を知らない! つまり a-b=a+(-b) , a-(-b)=a+b で処理。

2進数 00010100 に

00001100 を加えて

00100000 を得ることが出来ます。

10進数で見ますと

20-(-12) =20+12 =32 という計算をしました。

これが8ビットのレジスタに入っている。

これを右に3ビット算術シフトすると 1111 0011

これは、−13 の補数表現となっています。

回路図の青枠部分は、半加算回路です。この場合は出力Pがキャリフラグに相当します。 半加算回路が2つ使われていることがわかります。さて上記のA, Bは1ビットの0 か1 ですから、上は1ビット限りの加算です。数ケタの数の加算は上の全加算器を数個つなげます。 例えば8ビット(1バイト)で表す数どうしを加算するには、8個つなげていることになります。その接続の様子は後日図示する予定です(^_^)。

| A | B | C(k-1) | P | Q | Y | R | C(k) |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 | ||

| 1 | 0 | 0 | 1 | 1 | 0 | 0 | |

| 1 | 0 | 1 | 0 | 1 | 1 | ||

| 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 | 1 | 1 | ||

| 1 | 0 | 1 | 0 | 0 | 0 | 1 | |

| 1 | 1 | 0 | 1 | 0 | 1 |

下表はたし算 A+B のルールです。A=1, B=1 のとき 加算しているビットは0、繰り上がりの1

はキャりフラグにセットされるわけです。

| A | B | A+B |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 0 |

ゲート基本回路の話し(ハード的になります)

これまで数学ロジック的な面が多かったのですが、次はハード的(工学とか電気的)に考えてみます。例として一番分かりやすいMOSトランジスタで作るNOTゲートを取り上げましょう。 集積回路(IC)ではスイッチ要素として、トランジスタを利用し電圧をHigh、Low (あるいは On、Off) と変化させることにより、入出力を制御(せいぎょ)するのが殆どです。 ここでは代表的なMOS型トランジスタを使います。 MOSトランジスタはとても小さく1つのICチップに数万個も埋め込まれることもある程です。

(1)NOT(cMOS)

(1) In = 0ではpMOSが導電しOut = 1(Vdd接続)。

In = 1ではnMOSが導電しOut = 0 (GND接続)。

(2)NOT (nMOS)

(2) In = 0ではnMOSがOFFで、Out = 1(V接続)。

In = 1ではONに変わりOut = 0(0v接続)。

(3)NOT (pMOS)

(3)In = 0ではpMOSがONでOut = 1。

In = 1ではOFFに変わりOut = 0。

(1)(2)(3)いずれもNOTゲート回路であることが分かります。つまり入出力を反転させています。

Vddは電源(習慣的に+5v)、GNDはグランド (アースです = 0v )、Rは適当な抵抗、In=入力、Out=出力。

In に電圧が加えられていない状態では、pMOS トランジスタはON(=導電)、nMOSトランジスタはOFF です。逆に電圧が加えられると、pMOSはOFF、nMOSはON(=導電)になります。 トランジスタはスイッチと同じ働きをします。NOTゲートをインバータとも言います。<注> MOSトランジスタのゲート端子(左側)へは電流は発生しません。

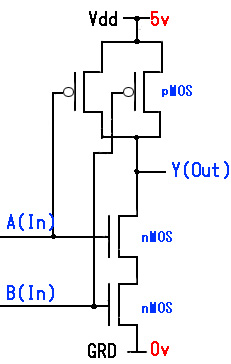

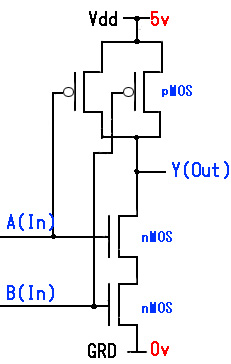

(4)NAND

NANDゲート回路は下図です。電源Vdd に近い2個の pMOSは並列になっており、GNDに近い nMOS2個は直列になっていることに注意し 、起こりうるすべての場合を表にしました。

| A | B | 上の並列pMOS側 | 下の直列nMOS側 | Y | |

| 0 | 0 | ON(2個とも導電) | OFF(2個とも) | 1 | =Vdd |

| 0 | 1 | ON(1個が導電) | OFF(1個は導電) | 1 | =Vdd |

| 1 | 0 | ON( 同上) | OFF( 同上) | 1 | =Vdd |

| 1 | 1 | OFF(2個とも) | ON(2個とも導電) | 0 | =GND |

同様にしてMOSトランジスタを使い、その他の基本ゲートAND、OR、XORを作ってみよう。多入力(3入力以上)の場合も考えてみよう。

IC(集積回路)の中をのぞく

NOT IC

6個のNOT回路を入れた14PINのIC

(1→2)

NAND IC

2入力のNAND 回路4個を入れた14PINのIC

(1,2→3)

その形からムカデ、ゲジゲジ虫とも呼びます。そのICの代表例を上に示しました。 コンピュータや携帯、電化製品の中にある半導体基板(はんどうたいきばん)に多数のIC(集積回路しゅうせきかいろ)が埋め込まれています。 殆どブラックボックス化しています。どのように利用するのでしょう。

実際に簡単な電子回路を作ってみました。

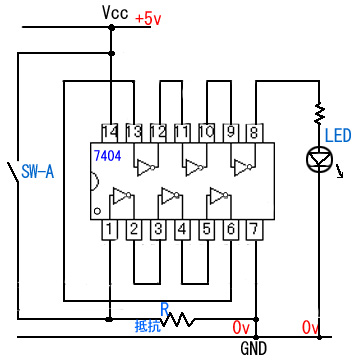

ブレッドボード(一種の半導体基板)上に各種パーツ、IC、コンデンサー、ダイオード、トランジスタ、コイル、抵抗などを並べて、さまざまな電子回路を実現するわけです。ここでは7404型という6個のNOT回路をもつ14PIN ICを図のように配線して実験を試みます。

ICを動作させるため電源を入れなければなりませんが、14番PIN=Vcc、7番PIN=GND と決められています。SW-A(スイッチA) をON (入力= 1) 、OFF (入力=0)と交互に切り替えると、LED(電球)が点灯(=1)、消灯(=0)を交互に繰り返す。ただそれだけです。これはICが良品か否かを検査するのに役立つというわけです。

問題です

上図において、電流の流れを確かめて、SW-AがON (1)のとき、 LEDが点灯(1)か、それとも消灯(0)か答えて下さい。ただ実験回路は上手く動作しなかった代物ですから信用無用で試さないでください(笑)。

答えは次のページへ。

前ページの情報処理試験問題の解説

問題1

2進数 11010000を右に2ビット算術シフトすると、最左端の符号ビットが 1であることに注意して、11010000→11110100 となります。2の補数で表されている負数です。この負数の絶対値(=正の数)を求めるため、

ビット列を反転して、1を加える操作をすると

11110100→00001011→00001100 となります。

問題の減算は、これを加算するということです。

コンピューターは減算を知らない! つまり a-b=a+(-b) , a-(-b)=a+b で処理。

2進数 00010100 に

00001100 を加えて

00100000 を得ることが出来ます。

10進数で見ますと

20-(-12) =20+12 =32 という計算をしました。

問題2

10進数の −100 は2の補数表現で 1001 1100これが8ビットのレジスタに入っている。

これを右に3ビット算術シフトすると 1111 0011

これは、−13 の補数表現となっています。

|

|

|

|